Описание

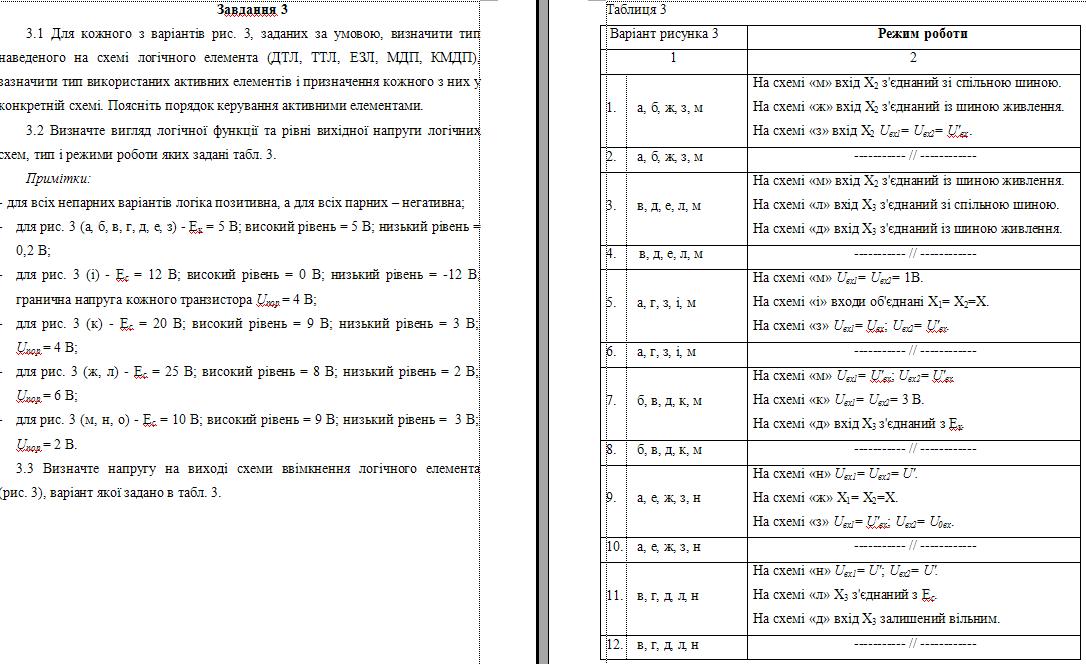

Завдання 3

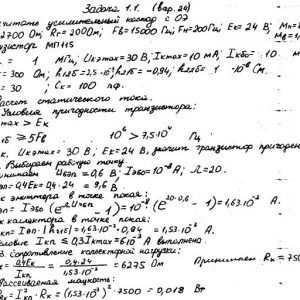

3.1 Для кожного з варіантів рис. 3, заданих за умовою, визначити тип наведеного на схемі логічного елемента (ДТЛ, ТТЛ, ЕЗЛ, МДП, КМДП), зазначити тип використаних активних елементів і призначення кожного з них у конкретній схемі. Поясніть порядок керування активними елементами.

3.2 Визначте вигляд логічної функції та рівні вихідної напруги логічних схем, тип і режими роботи яких задані табл. 3.

Примітки:

— для всіх непарних варіантів логіка позитивна, а для всіх парних – негативна;

— для рис. 3 (а, б, в, г, д, е, з) — Ек = 5 В; високий рівень = 5 В; низький рівень = 0,2 В;

— для рис. 3 (і) — Ес = 12 В; високий рівень = 0 В; низький рівень = -12 В; гранична напруга кожного транзистора Uпор = 4 В;

— для рис. 3 (к) — Ес = 20 В; високий рівень = 9 В; низький рівень = 3 В; Uпор = 4 В;

— для рис. 3 (ж, л) — Ес = 25 В; високий рівень = 8 В; низький рівень = 2 В; Uпор = 6 В;

— для рис. 3 (м, н, о) — Ес = 10 В; високий рівень = 9 В; низький рівень = 3 В; Uпор = 2 В.

3.3 Визначте напругу на виході схеми ввімкнення логічного елемента (рис. 3), варіант якої задано в табл. 3.

Варіант рисунка 3 варіант 5 а, г, з, і, м

Режим роботи

На схемі «м» Uвх1= Uвх2= 1В.

На схемі «і» входи об’єднані Х1= Х2=Х.

На схемі «з» Uвх1= Uвх; Uвх2= U’вх.

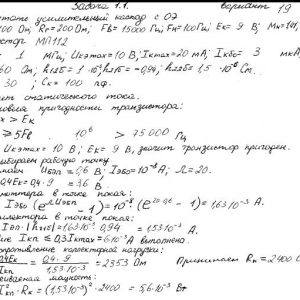

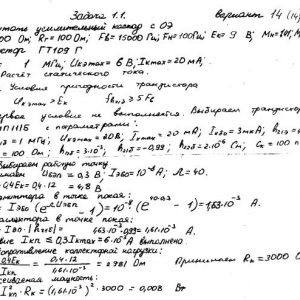

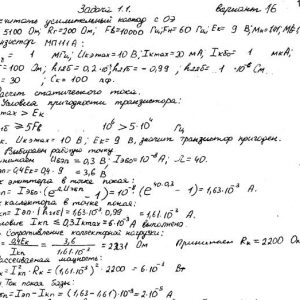

Методичка по электронике и микросхемотехнике

метод одна задача 3